3月3日,芯片制造商英特尔、台积电、三星联合日月光、AMD、ARM、高通、谷歌、微软、Meta(Facebook)等十家行业巨头共同宣布,成立小芯片(Chiplet)联盟,并推出一个全新的通用芯片互联标准――Ucle,以此共同打造小芯片互联标准,推动开放生态建设。

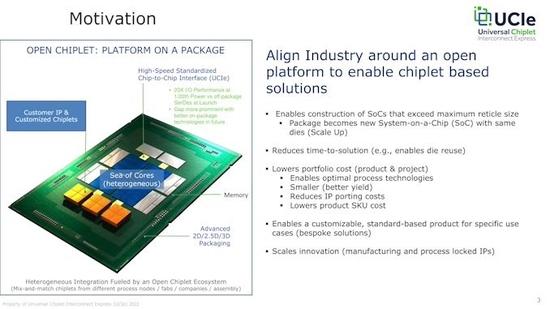

新联盟旨在建立一个名为Universal Chiplet Interconnect Express(UCIe)的单芯片封装标准,以创建新的生态系统并促进封装和堆叠领域的合作。简而言之,他们将讨论将不同类型的芯片(或所谓的小芯片)组合在一个封装中以创建更强大的芯片系统的更好方法。

“UCIe旨在提供完整的‘die-to-die’互连标准,使最终用户可以轻松混合和匹配小芯片组件。这意味着他们将能够使用来自不同供应商的部件构建定制的片上系统(SoC)。单个芯片在封装之前被称为裸片,”报告补充道。

鉴于芯片巨头似乎希望在芯片封装标准上合作,这反映了该领域日益增长的重要性。鉴于芯片上可以容纳的晶体管数量有限,公司现在正试图通过以各种组合方式封装和堆叠芯片来优化其产品的性能。

英特尔在发言中表示:“将多个小芯片集成在一个封装中以提供跨细分市场的产品是半导体行业的未来,也是英特尔IDM 2.0战略的支柱。对这一未来至关重要的是一个开放的小芯片生态系统,主要行业合作伙伴将在UCIe联盟下共同努力,实现改变行业交付新产品的方式,并继续兑现摩尔定律承诺的共同目标。”

对此,国外专家解释称,SoC芯片已经陷入研发瓶颈期,芯片精密度越来越高,也意味着技术跃迁变得越来越难。尽管各大厂商快马加鞭,但原本计划在2021年底就上市的3nm芯片,依旧一拖再拖遥遥无期,摩尔定律已经失效了。并且根据半导体技术研究机构Semiengingeering统计数据显示,在7nm节点上,芯片的开发费用约为2.97亿美元,而到了5nm节点,芯片的研发费用就已经达到了5.42亿美元,上涨了足足82%,未来3nm如果依旧坚持SoC技术,研发费用很可能超过10亿美元,因此技术变革势在必行。

http:www.cps800.com/news/63744.htm