对于电源管理IC,把包括开关、控制和无源元件在内的整个电源安装在一块芯片上,就能促成更高的功率效率,并降低散热量。尖端的电源拓扑结构、微型磁性元件、更快的开关器件可以共同使单片电源成为现实。

要点

* 微型单片电源能在电子器件中促成更高效的电源管理和更低的散热量。

* 对于两三兆赫的速度而言,单一封装即可容纳的电源已成为现实。

* 磁性元件和开关器件必须不断进步,来促成电源电路的持续微型化。

请想象一种手机电池,它能供应无线电力,并仍适合目前的形状系数。对于目前的便携电子设备的最大缺点而言,它堪称完美的解决方案,不是吗?答案是否定的。即便有这种魔幻般的电池,人们仍面临功耗问题:在目前的电源管理方案下,手机很快就会变得烫手。关键在于有效功率,而非可用功率。在寻找日益高效的电源方案的过程中,浮现出了包含电源转换、稳压、管理、无源元件在内的电源SOC(单片电源)概念,它已成为人们渴求的目标。一些电源公司和大学研究人员正在探求这种技术。电源SOC不仅将使手持电子设备受益,还将惠及笔记本电脑(电池寿命会更长)和服务器(能源成本会更低)。在未来若干年,这些电源SOC将对各类电子应用产生吸引力。

目前带有外部电感器的DC/DC PMU(电源管理单元)IC已经比几年前的原有器件小了许多。例如,Analog Devices公司的6 MHz ADP2121转换器也依靠外部电感器,包括电感器在内的尺寸仅5 mm2。核心作为目前ASIC的一部分日益普及,这推动了一种需求,即进一步缩小电源控制电路,使之进入电源SOC中。例如,一部手机可能有四根或更多天线,其中包括蓝牙、CDMA、GSM通信、3G单元,还含有视频和基带射频部分。为了确保功率效率,每颗核心均须快速通断,否则系统会在未使用的核心上浪费功率。为实现精细的电源控制,每颗核心均需要自己的DC电压源,其中包括电压转换与稳定。但是,四个或更多PMU安装在一颗多核芯片周围,会使该芯片相形见绌,即便它们每个的尺寸仅有5 mm2。

人们也许会考虑在板上装几个电源模块,并用半导体开关来通断核心和子块。但是,电源很难在其整个负载范围(一般是10%至90%)均保持高效。若主电源多数时间都用于低电流负载范围,那么它的功率效率会较低,产生的系统热量会更多。

电源SOC技术缺乏两种主要部件:高效合算的开关器件、工作于20MHz至100MHz或更高频率的磁性元件。射频领域的确存在超高速开关器件,但其开发者通常把外来半导体元件作为其基础,没有使用廉价的芯片工艺。设计者也已为射频领域开发了磁性元件,但其用途一直是辐射功率。电源应用的需求恰好相反——安静的非辐射器件。另外,磁性元件研究一直比较冷清。只要高速开关器件不能实用,就不会有人需要高速磁性元件。

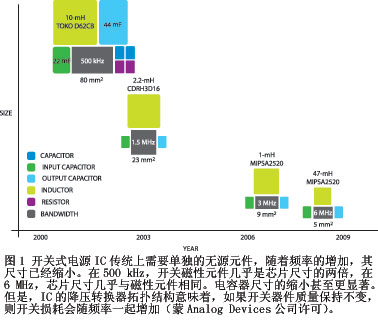

为了理解改用20MHz、100MHz或更高开关频率的重要性,请看看更高的开关速度对目前PMU尺寸的影响(图1)。在500 kHz,开关磁性元件几乎是芯片尺寸的两倍。在目前大约1MHz的开关频率,PMU的无源元件的尺寸几乎与电源控制及稳压电路相当。在6 MHz,芯片尺寸几乎与磁性元件相同。电容器尺寸的缩小甚至更显著。电源SOC的支持者们暗示:在20 MHz至100 MHz或更高速度时,无源元件会明显缩小,可以把它们放在控制电子器件的混合信号晶粒上。

考克大学丁铎尔国家研究所电源磁性元件研究人员Cian Mathúna博士预言:包含集成电感器在内的完整电源SOC很快将能安装于仅为1 mm2的空间中,其中包括PSIP(电源系统级封装)内的电源控制晶圆上的晶圆级微型电感器。从BOM(材料清单)角度看,PSIP和电源SOC之间几乎没有区别:如果拆开PSIP,人们就会看到硅开关器件和控制电路位于一块IC中,而磁性元件和电容器则位于另外一两个器件中——所有元件均位于同一封装中。虽然PSIP器件没有利用晶圆级装配更低的成本和更高的可靠性,但它们的确满足了各种应用对小零件、更低BOM成本、更简单组装的需求。包括Vicor、Linear Technology、Enpirion在内的几家公司已开始采用这种方法。

例如,Enpirion公司的1 MHz、600 mA EP5368Q集成了一个电感器,安装在3 mm × 3 mm × 1.1 mm QFN封装中,并且总尺寸仅为22 mm2,其中包括两个外部电容器。该公司提供多种可达9 A电流和5 MHz开关速度的器件。Enpirion公司把开关与控制电路和电感器分离开来,并在同一封装内放置了两颗晶粒。该公司产品营销总监Michael Laflin表示,公司可以把电感器装配在硅晶圆上,或装配在更传统的多层螺旋结构中,这取决于应用需求。这些需求包括负载电流、电感、损耗预算、饱和电流等因素。该公司还考虑了以下事实:不同磁性材料在不同频率表现出不同损耗特征和行为,因此磁性材料在电感器设计领域也有一席之地。Enpirion公司不愿透露其电感器背后的技术,这是因为磁性元件技术是其器件中的“秘笈”。

今年1月,Enpirion公司在爱尔兰考克举行的PwrSOC (Power-SOC)专题讨论会上宣读了一篇论文,详细介绍了它在可制造性、成品率、可靠性、成本方面接受的教训(参考文献1)。这些平淡无奇的决定因素是产品开发取得成功的关键,这是因为在电源管理领域,正如Laflin所说,“成本决定一切。”

爱尔兰考克大学的丁铎尔国家研究所是最有经验的晶圆级磁性元件研究中心之一,它利用其4英寸晶圆加工线来研究开关频率为10 MHz至100 MHz的电感器(图2a)。这些电感器使用“跑道式”几何结构的电镀铜绕组,后者被封装在一种薄膜电镀密封镍铁软磁芯中(参考文献2)。为了提供参考,丁铎尔的研究人员用一块单片MOSFET及驱动器传动系IC演示了工作于15 MHz至65 MHz的电感器。这种降压转换器SMPS(开关式电源)包含转换器和电感器,在20 MHz时的效率为80%,使用了Coilcraft公司(www.coilcraft.com)的商用贴片电感器,并且输入电压为3V,输出电压为1.5V,输出电流为100 mA。当研究人员替换了Tyndall 2.5 mm2微电感器之后,效率降至76%。但请记住:Tyndall电感器不是为该电路设计的,它本是某种生产设计的一部分。Mathúna表示,研究人员可以调整铜损耗和磁芯损耗。他说:“我们把铜绕组电镀到模具中,厚度为35 m至50 ?m。如果我们增加铜的厚度,我们就能在很大程度上仿真Coilcraft电感器。另外,磁芯材料有自己的内在损耗。在镀于薄膜的磁性材料中,电阻系数将会很低,即这些材料将会具有很强的导电能力。例如,某种镍铁材料的电阻系数约为45 Ωcm。如果我们改用另一种系数接近100 至150 Ωcm的磁性材料,我们就能降低涡流损耗。”

电源SOC开发工作中的另一个症结是高速开关器件。降压转换器体系结构是目前最常用的DC/DC-SMPS拓扑结构,在效率和开关频率之间是负相关:开关频率每提高一次,效率最初都会下降。德州仪器公司(TI)电源管理产品业务的产品线经理Ted Thomas说:“如果你的设计方案的开关频率是5 MHz,并且把它提高至20 MHz,那么开关损耗至少将是以前的四倍。开关损耗最终会支配电源效率。”

但是,有几种拓扑结构的开关频率和低效率之间的关系较弱。以ZVS(零电压开关)拓扑结构为例,开关器件仅在其两端没有电压时通断。可使用电路的谐振频率来确定零电压点。设计者们多年来一直在AC/DC电源中使用ZVS,这些电源必须容纳大电流。这些开关损耗很低的拓扑结构的问题在于其复杂性。但如果制造商们能把它们装在“黑盒”电源SOC中,并且为设计方案配比了合适的磁性元件,那么对于电路设计者而言,它们就能变成直截了当的构件。

还可选择一些采用非传统工艺的技术,它们目前可供设计者探索更快的开关器件。例如,碳化硅能以较低的损耗支持很高的开关速率,但它较高的成本可能会使它无法用于主流的成本敏感型器件。International Rectifier公司9月宣布了它的氮化镓平台,它宣称这种半导体工艺具有“改变游戏规则的”较高功率密度。该公司声称:它的技术优势在于它能使用廉价、货源充足的硅晶圆来构建电路。该方法在不牺牲性能的前提下降低了成本。与未采用硅的氮化镓产品相比,这些器件还能在高得多的电压完成开关动作。International Rectifier公司计划年底之前开始发运这些器件的样品,工作频率低于6 MHz至10 MHz。

电源SOC未来还会发生哪些事情?10MHz PSIP和100MHz PSIP将分别在未来18个月和三至五年内出现,二者都将采用标准的硅工艺。

参考文献

1. International Workshop on Power Supply on Chip, Cork, Ireland, www.powersoc.org/programme.html.

2. Tyndall, www.tyndall.ei.

http:www.cps800.com/news/2009-2/2009241837.html