随着技术的进步,EMI 对电路正常运行构成越来越大的威胁。这是因为电子应用正转向各种无线通信或者便携式平台。因此大多数干扰 EMI 信号最终都以传导 EMI 的形式进入到 PCB 线迹(trace)中。

当您努力想要设计出一种抗 EMI 电路时,您会发现,模拟传感器电路往往会成为巨大的 EMI 吸收器。这是因为,传感器电路常常产生低电平信号,并且有许多高阻抗模拟端口。另外,这些电路使用更加紧凑的组件间隔,其让系统更容易截获和传导噪声干扰,从而进入到线迹中。

在这种 EMI 情况下,运算放大器 (op amp) 便会成为一个主要目标。我们在本系列文章的第1部分“EMI 如何通过介质干扰电路”看到了这种效应,此文中图 1 所示 EMI 信号引起 1.5 伏的偏移电压误差!

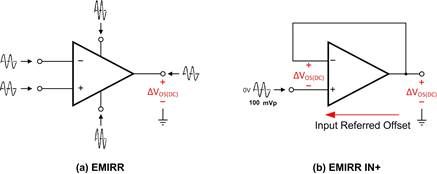

一个标准的运算放大器有 3 个低阻抗引脚(正功率、负功率和输出)以及 2 个高阻抗输入引脚(请参见图 1a)。尽管这些引脚可以抵抗 EMI 影响,但是输入引脚最为脆弱。

图 1 EMIRR 与 EMIRR IN+ 测定方法比较

EMIRR 电磁干扰抑制比

电压反馈放大器的反相和非反相引脚的特性基本相同。但是,非反相输入(请参见图 1b)的放大器 EMI 耐受度测试最为简单。

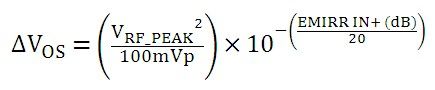

方程式 1

方程式 1 中,VRF_PEAK 为所用 RF 电压的峰值,VOS 为放大器的 DC 偏移电压,而 100 mVP 为 100 mVP 输入信号 EMIRR IN+ 参考。

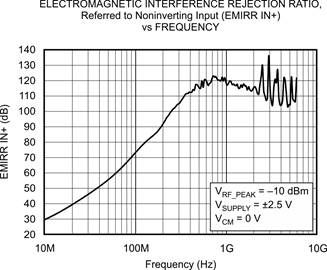

您可以利用 EMIRR 衡量标准,比较放大器的 EMI 抑制性能。图 2 显示了 TI OPA333 CMOS 运算放大器的 EMIRR IN+ 响应。该图表明,这种器件可以较好地抑制器件300 kHz带宽以上的频率信号。

- 1

- 2

- 总2页

来源:互联网

http:www.cps800.com/news/2012-11/20121116164210.html