许多系统需要可靠的非易失性存储,对于这些系统,可选择EEPROM存储器技术。EEPROM技术具有稳定可靠的架构,供应商较多,并且经过了多年的改进。EEPROM器件可用于各种工业标准串行总线,包括I2C?、SPI、Microwire和UNI/O总线。其中,I2C总线在单片机和其他芯片组中具有广泛的硬件支持,并且信号传递方式简单,可采用极小的硅片有效实现,因此占据了非易失性存储器市场约70%的份额。但是,I2C总线拓扑要依赖于阻值合适的上拉电阻才能实现稳定可靠的通信。电阻值选择错误不仅会造成电能浪费,还可能导致总线状态和传输过程由于噪声、温度变化、工作电压变化以及器件间的制造差异而出错。

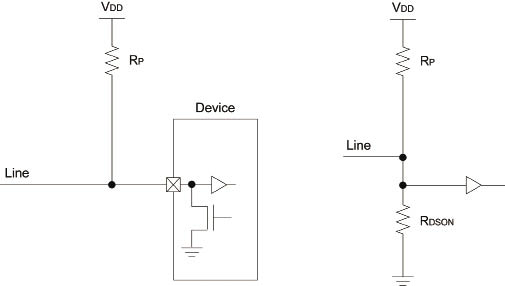

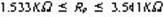

I2C是二线同步总线,使用总线主器件SCL线上产生的信号作为时钟。SDA线用于双向数据传输。当时钟处于特定状态时可修改数据线,以指示传输的开始和停止,从而避免使用更多的线。I2C总线以集电极开路输出为基础,其中,器件可通过接地晶体管拉低线的电平,如图1所示。这样便可轻松对总线控制进行仲裁,从而在一条数据线上实现双向通信以及多主器件支持。如图1所示,每条线都有一个外部电阻连接至Vdd,该电阻可在释放总线或总线空闲时拉高线的电平。

图1 I2C?总线拓扑

确定上拉电阻值(Rp)时需要考虑三个因素:

・ 电源电压(Vdd)

・ 总线总电容(CBUS)

・ 高电平总输入电流(IIH)

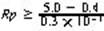

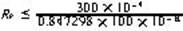

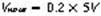

以下面的条件为例计算理想的上拉电阻值:

・ 电源电压(Vdd)为5V

・ 时钟频率为400kHz

・ 总线电容为100pF

电源电压(Vdd)

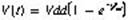

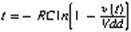

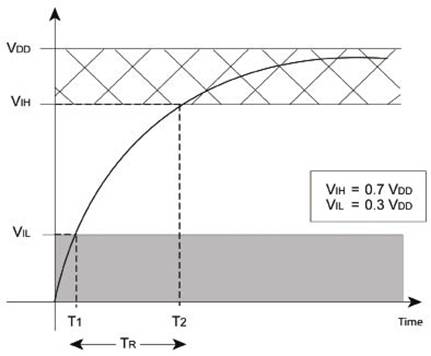

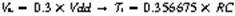

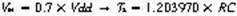

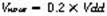

I2C规范将低于VIL或低于电源电压30%的电压定义为逻辑低电平,同样,将高于VIH或高于电源电压70%的电压定义为逻辑高电平,如图2所示。这两个电平之间的电压属于不明确的逻辑电平。实际上,引脚会将该范围内的电平读为逻辑高电平或逻辑低电平,但在器件间可能不同,因为温度、电压、噪声源和其他环境因素会影响逻辑电平。

图2 指定为逻辑高电平和逻辑低电平的电压电平

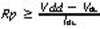

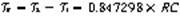

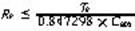

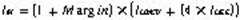

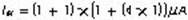

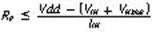

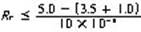

电源电压限制了可允许总线拉低的最小Rp值。过强的上拉会阻止器件充分拉低线的电平,导致无法确保逻辑低电平能被检测到。这是由上拉电阻与接地晶体管的导通电阻之间形成的分压器产生的,如图3所示。通常不会指定晶体管的导通电阻。相反,会给定使晶体管上的电压降低于输出逻辑低电压电平(VOL)的最大灌电流(IOL)。使用欧姆定律得出公式1。

- 1

- 2

- 3

- 总3页

来源:互联网

http:www.cps800.com/news/36225.htm